#### **UNIT-III**

#### **COMBINATIONAL CIRCUITS**

#### **Combinational Logic**

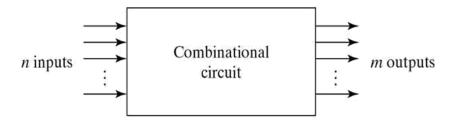

- Logic circuits for digital systems may be combinational or sequential.

- A combinational circuit consists of input variables, logic gates, and output variables.

For n input variables, there are 2<sup>n</sup> possible combinations of binary input variables. For each possible input Combination, there is one and only one possible output combination. A combinational circuit can be described by m Boolean functions one for each output variables. Usually the input s comes from flip-flops and outputs goto flip-flops.

#### **Design Procedure:**

- 1. The problem is stated

- 2. The number of available input variables and required output variables is determined. 3.The input and output variables are assigned lettersymbols.

- 4. The truth table that defines the required relationship between inputs and outputs is derived.

- 5. The simplified Boolean function for each output is obtained.

#### Adders:

Digital computers perform variety of information processing tasks, the one is arithmetic operations. And the most basic arithmetic operation is the addition of two binary digits. i.e, 4 basic possible operations are:

$$0+0=0,0+1=1,1+0=1,1+1=10$$

The first three operations produce a sum whose length is one digit, but when augends and addend bits are equal to 1,the binary sum consists of two digits. The higher significant bit of this result is called a carry. A combinational circuit that performs the addition of two bits is called a half-adder. One that performs the addition of 3 bits (two significant bits & previous carry) is called a full adder. & 2 half adder can employ as a full-adder.

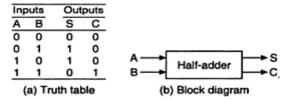

**The Half Adder**: A Half Adder is a combinational circuit with two binary inputs (augends and addend bits and two binary outputs (sum and carry bits.) It adds the two inputs (A and B) and produces the sum (S) and the carry (C) bits. It is an arithmetic operation of addition of two single bit words.

The Sum(S) bit and the carry (C) bit, according to the rules of binary addition, the sum (S) is the X-OR of A and B (It represents the LSB of the sum). Therefore,

$$S=A + A \oplus B$$

The carry (C) is the AND of A and B (it is 0 unless both the inputs are 1). Therefore,

$$C=AB$$

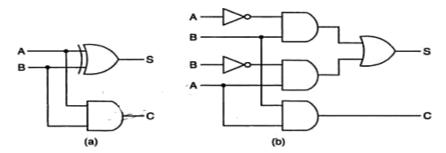

A half-adder can be realized by using one X-OR gate and one AND gate a

Logic diagrams of half-adder

#### NAND LOGIC:

$$S = A\overline{B} + \overline{A}B = A\overline{B} + A\overline{A} + \overline{A}B + B\overline{B}$$

$$= A(\overline{A} + \overline{B}) + B(\overline{A} + \overline{B})$$

$$= A \cdot \overline{AB} + B \cdot \overline{AB}$$

$$= \overline{A \cdot \overline{AB} \cdot B \cdot \overline{AB}}$$

$$C = AB = \overline{AB}$$

$$A \cdot \overline{AB} \cdot \overline{AB} \cdot \overline{AB} \cdot \overline{AB}$$

$$B \cdot \overline{AB} \cdot \overline{AB} \cdot \overline{AB} \cdot \overline{AB}$$

Logic diagram of a half-adder using only 2-input NAND gates.

NOR Logic:

$$S = A\overline{B} + \overline{A}B = A\overline{B} + A\overline{A} + \overline{A}B + B\overline{B}$$

$$= A(\overline{A} + \overline{B}) + B(\overline{A} + \overline{B})$$

$$= (A + B)(\overline{A} + \overline{B})$$

$$= \overline{A + B} + \overline{\overline{A} + \overline{B}}$$

$$C = AB = \overline{AB} = \overline{A} + \overline{B}$$

$$A = \overline{A} + \overline{B}$$

$$A = \overline{A} + \overline{B}$$

$$A = \overline{A} + \overline{B}$$

Logic diagram of a half-adder using only 2-input NOR gates.

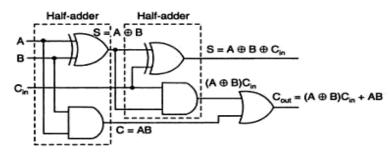

#### The Full Adder:

A Full-adder is a combinational circuit that adds two bits and a carry and outputs a sum bit and a carry bit. To add two binary numbers, each having two or more bits, the LSBs can be added by using a half-adder. The carry resulted from the addition of the LSBs is carried over to the next significant column and added to the two bits in that column. So, in the second and higher columns, the two data bits of that column and the carry bit generated from the addition in the previous column need to be added.

The full-adder adds the bits A and B and the carry from the previous column called the carry-in  $C_{in}$  and outputs the sum bit S and the carry bit called the carry-out  $C_{out}$ . The variable S gives the value of the least significant bit of the sum. The variable  $C_{out}$  gives the output carry. The

eight rows under the input variables designate all possible combinations of 1s and 0s that these variables may have. The 1s and 0s for the output variables are determined from the arithmetic sum of the input bits. When all the bits are 0s, the output is 0. The S output is equal to 1 when only 1 input is equal to 1 or when all the inputs are equal to 1. The  $C_{out}$  has a carry of 1 if two or three inputs are equal to 1.

|   | Inputs | 5        | Sum      | Carry |                                  |

|---|--------|----------|----------|-------|----------------------------------|

| Α | В      | Cin      | S        | Cout  |                                  |

| 0 | 0      | 0        | 0        | 0     |                                  |

| 0 | 0      | 1        | 1        | 0     |                                  |

| 0 | 1      | 0        | 1        | 0     |                                  |

| 0 | 1      | 1        | 0        | 1     |                                  |

| 1 | 0      | 0        | 1        | 0     |                                  |

| 1 | 0      | 1        | 0        | 1     | A → S                            |

| 1 | 1      | 0        | 0        | 1     | B → Full-adder                   |

| 1 | 1      | 1        | 1        | 1     | C <sub>in</sub> → C <sub>o</sub> |

|   |        | (a) Trut | th table |       | (b) Block diagram                |

|   |        |          |          |       | Full-adder.                      |

From the truth table, a circuit that will produce the correct sum and carry bits in response to every possible combination of A,B and C<sub>in</sub> is described by

$$S = \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}}$$

$$C_{out} = \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}} + \overrightarrow{ABC_{in}}$$

and

$$S = A \qquad B \qquad C_{in}$$

$$C_{out} = AC_{in} + BC_{in} + AB$$

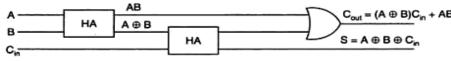

The sum term of the full-adder is the X-OR of A,B, and C<sub>in</sub>, i.e, the sum bit the modulo sum of the data bits in that column and the carry from the previous column. The logic diagram of the full-adder using two X-OR gates and two AND gates (i.e, Two half adders) and one OR gate

Logic diagram of a full-adder using two half-adders.

The block diagram of a full-adder using two half-adders is

Block diagram of a full-adder using two half-adders.

Even though a full-adder can be constructed using two half-adders, the disadvantage is that the bits must propagate through several gates in accession, which makes the total propagation delay greater than that of the full-adder circuit using AOI logic.

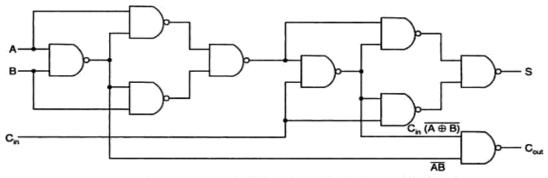

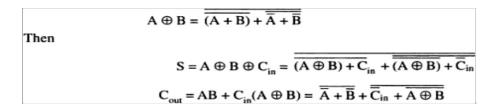

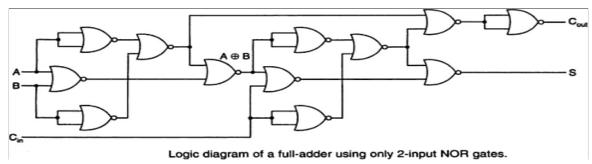

The Full-adder neither can also be realized using universal logic, i.e., either only NAND gates or only NOR gates as

$$A \oplus B = \overline{A \cdot \overline{AB} \cdot B \cdot \overline{AB}}$$

Then

$$S = A \oplus B \oplus C_{in} = \overline{(A \oplus B) \cdot \overline{(A \oplus B)C_{in}} \cdot \overline{C_{in} \cdot \overline{(A \oplus B)C_{in}}}}$$

NAND Logic:

$$C_{out} = C_{in}(A \oplus B) + AB = \overline{C_{in}(A \oplus B) \cdot AB}$$

$$\overline{A}$$

$$B$$

$$C_{in}$$

$$A$$

$$B$$

$$C_{in}$$

Sum and carry bits of a full-adder using AOI logic.

Logic diagram of a full-adder using only 2-input NAND gates.

#### **Subtractors:**

The subtraction of two binary numbers may be accomplished by taking the complement of the subtrahend and adding it to the minuend. By this, the subtraction operation becomes an addition operation and instead of having a separate circuit for subtraction, the adder itself can be used to perform subtraction. This results in reduction of hardware. In subtraction, each subtrahend bit of the number is subtracted from its corresponding significant minuend bit to form a difference bit. If the minuend bit is smaller than the subtrahend bit, a 1 is borrowed from the next significant position., that has been borrowed must be conveyed to the next higher pair of bits by means of a signal coming out (output) of a given stage and going into (input) the next higher stage.

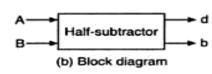

#### The Half-Subtractor:

A Half-subtractor is a combinational circuit that subtracts one bit from the other and produces the difference. It also has an output to specify if a 1 has been borrowed. . It is used to subtract the LSB of the subtrahend from the LSB of the minuend when one binary number is subtracted from the other.

A Half-subtractor is a combinational circuit with two inputs A and B and two outputs d and b. d indicates the difference and b is the output signal generated that informs the next stage that a 1 has been borrowed. When a bit B is subtracted from another bit A, a difference bit (d) and a borrow bit (b) result according to the rules given as

| Inp | uts      | Out     | puts |

|-----|----------|---------|------|

| A   | В        | d       | b    |

| 0   | 0        | 0       | -0   |

| 1   | 0        | 1       | 0    |

| 1.  | 1        | 0       | О    |

| 0   | 1        | 1       | 1    |

| - 1 | (a) Trut | h table |      |

|     |          |         |      |

Half-subtractor.

The output borrow b is a 0 as long as  $A \ge B$ . It is a 1 for A = 0 and B = 1. The d output is the result of the arithmetic operation 2b + A - B.

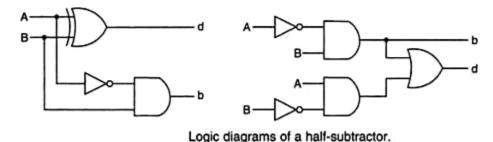

A circuit that produces the correct difference and borrow bits in response to every possible combination of the two 1-bit numbers is , therefore ,

$$d=A + A \oplus B$$

and  $b= B$

That is, the difference bit is obtained by X-OR ing the two inputs, and the borrow bit is obtained by ANDing the complement of the minuend with the subtrahend. Note that logic for this exactly the same as the logic for output S in the half-adder.

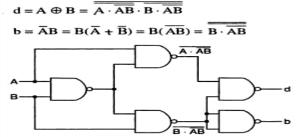

A half-substractor can also be realized using universal logic either using only NAND gates or using NOR gates as:

#### NAND Logic:

Logic diagram of a half-subtractor using only 2-input NAND gates.

#### NOR Logic:

$$d = A \oplus B = A\overline{B} + \overline{A}B = A\overline{B} + B\overline{B} + \overline{A}B + A\overline{A}$$

$$= \overline{B}(A + B) + \overline{A}(A + B) = \overline{B + \overline{A + B} + \overline{A + A + B}}$$

$$d = \overline{A}B = \overline{A}(A + B) = \overline{\overline{A}(A + B)} = \overline{A + (\overline{A + B})}$$

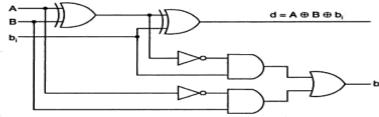

#### The Full-Subtractor:

The half-subtractor can be only for LSB subtraction. IF there is a borrow during the subtraction of the LSBs, it affects the subtraction in the next higher column; the subtrahend bit is subtracted from the minuend bit, considering the borrow from that column used for the subtraction in the preceding column. Such a subtraction is performed by a full-subtractor. It subtracts one bit (B) from another bit (A), when already there is a borrow bi from this column for the subtraction in the preceding column, and outputs the difference bit (d) and the borrow bit(b) required from the next d and b. The two outputs present the difference and output borrow. The 1s and 0s for the output variables are determined from the subtraction of A-B-bi.

| Ir | Inputs Difference |    | nputs Difference Born |   | Borrow            |  |

|----|-------------------|----|-----------------------|---|-------------------|--|

| Ā  | В                 | b  | d                     | ь |                   |  |

| 0  | 0                 | 0  | 0                     | 0 |                   |  |

| 0  | 0                 | 1  | 1                     | 1 |                   |  |

| 0  | 1                 | 0  | 1                     | 1 |                   |  |

| 0  | 1                 | 1  | 0                     | 1 |                   |  |

| 1  | 0                 | 0  | 1                     | 0 |                   |  |

| 1  | 0                 | 1  | 0                     | 0 | A                 |  |

| 1  | 1                 | 0  | 0                     | 0 | B Full-subtractor |  |

| 1  | 1                 | 1  | 1                     | 1 | b,                |  |

|    |                   | (8 | a) Truth table        |   | (b) Block diagram |  |

|    |                   |    |                       |   | Full-subtractor.  |  |

From the truth table, a circuit that will produce the correct difference and borrow bits in response to every possible combinations of A,B and bi is

$$d = \overline{A}\overline{B}b_i + \overline{A}B\overline{b}_i + A\overline{B}\overline{b}_i + ABb_i$$

$$= b_i(AB + \overline{A}\overline{B}) + \overline{b}_i(A\overline{B} + \overline{A}B)$$

$$= b_i(\overline{A} \oplus \overline{B}) + \overline{b}_i(A \oplus B) = A \oplus B \oplus b_i$$

and

$$b = \overline{A}\overline{B}b_i + \overline{A}B\overline{b}_i + \overline{A}Bb_i + ABb_i = \overline{A}B(b_i + \overline{b}_i) + (AB + \overline{A}\overline{B})b_i$$

$$= \overline{A}B + (\overline{A} \oplus \overline{B})b_i$$

A full-subtractor can be realized using X-OR gates and AOI gates as

Logic diagram of a full-subtractor.

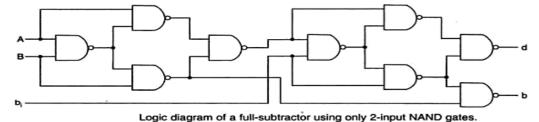

The full subtractor can also be realized using universal logic either using only NAND gates or using NOR gates as:

#### NAND Logic:

$$d = A \oplus B \oplus b_{i} = \overline{(A \oplus B) \oplus b_{i}} = \overline{(A \oplus B)(\overline{A \oplus B})b_{i}} \cdot \overline{b_{i}} \overline{(A \oplus B)b_{i}}$$

$$b = \overline{AB} + b_{i} \overline{(A \oplus B)} = \overline{\overline{AB} + b_{i}} \overline{(\overline{A \oplus B})}$$

$$= \overline{\overline{AB} \cdot \overline{b_{i}} \overline{(\overline{A \oplus B})}} = \overline{\overline{B(\overline{A} + \overline{B})} \cdot \overline{b_{i}} \overline{(\overline{b_{i}} + (\overline{A \oplus B}))}}$$

$$= \overline{\overline{B \cdot \overline{AB}} \cdot \overline{b_{i}} \overline{[\overline{b_{i}} \cdot (\overline{A \oplus B})]}}$$

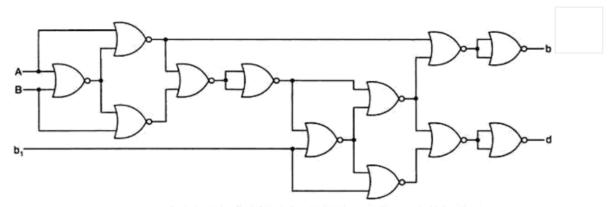

#### NOR Logic:

$$d = A \oplus B \oplus b_{i} = \overline{(A \oplus B) \oplus b_{i}}$$

$$= \overline{(A \oplus B)b_{i} + \overline{(A \oplus B)b_{i}}}$$

$$= \overline{[(A \oplus B) + \overline{(A \oplus B)b_{i}}][b_{i} + \overline{(A \oplus B)b_{i}}]}$$

$$= \overline{(A \oplus B) + \overline{(A \oplus B) + b_{i}}} + \overline{b_{i} + \overline{(A \oplus B) + b_{i}}}$$

$$= \overline{(A \oplus B) + \overline{(A \oplus B) + b_{i}}} + \overline{b_{i} + \overline{(A \oplus B) + b_{i}}}$$

$$= \overline{(A \oplus B) + \overline{(A \oplus B) + b_{i}}} + \overline{b_{i} + \overline{(A \oplus B) + b_{i}}}$$

$$b = \overline{AB} + b_{i} \overline{(A \oplus B)}$$

$$= \overline{A(A + B) + \overline{(A \oplus B)}[(A \oplus B) + b_{i}]}$$

$$= \overline{A + \overline{(A + B)} + \overline{(A \oplus B) + \overline{(A \oplus B) + b_{i}}}}$$

Logic diagram of a full subtractor using only 2-input NOR gates.

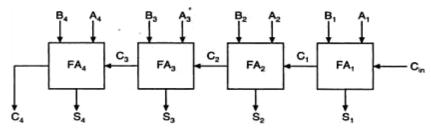

#### **Binary Parallel Adder:**

A binary parallel adder is a digital circuit that adds two binary numbers in parallel form and produces the arithmetic sum of those numbers in parallel form. It consists of full adders connected in a chain , with the output carry from each full-adder connected to the input carry of the next full-adder in the chain.

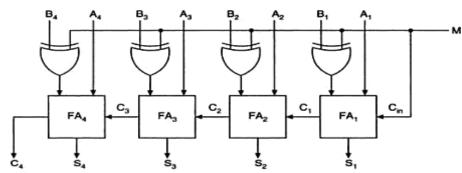

The interconnection of four full-adder (FA) circuits to provide a 4-bit parallel adder. The augends bits of A and addend bits of B are designated by subscript numbers from right to left, with subscript 1 denoting the lower –order bit. The carries are connected in a chain through the full-adders. The input carry to the adder is C<sub>in</sub> and the output carry is C4. The S output generates the required sum bits. When the 4-bit full-adder circuit is enclosed within an IC package, it has four terminals for the augends bits, four terminals for the addend bits, four terminals for the sum bits, and two terminals for the input and output carries. AN n-bit parallel adder requires n-full adders. It can be constructed from 4-bit, 2-bit and 1-bit full adder ICs by cascading several packages. The output carry from one package must be connected to the input carry of the one with the next higher –order bits. The 4-bit full adder is a typical example of an MSI function.

Logic diagram of a 4-bit binary parallel adder.

#### Ripple carry adder:

In the parallel adder, the carry –out of each stage is connected to the carry-in of the next stage. The sum and carry-out bits of any stage cannot be produced, until sometime after the carry-in of that stage occurs. This is due to the propagation delays in the logic circuitry,

which lead to a time delay in the addition process. The carry propagation delay for each full-adder is the time between the application of the carry-in and the occurrence of the carry-out.

The 4-bit parallel adder, the sum (S<sub>1</sub>) and carry-out (C<sub>1</sub>) bits given by FA<sub>1</sub> are not valid, until after the propagation delay of FA<sub>1</sub>. Similarly, the sum S<sub>2</sub> and carry-out (C<sub>2</sub>) bits given by FA<sub>2</sub> are not valid until after the cumulative propagation delay of two full adders (FA<sub>1</sub> and FA<sub>2</sub>), and so on. At each stage ,the sum bit is not valid until after the carry bits in all the preceding stages are valid. Carry bits must propagate or ripple through all stages before the most significant sum bit is valid. Thus, the total sum (the parallel output) is not valid until after the cumulative delay of all the adders.

The parallel adder in which the carry-out of each full-adder is the carry-in to the next most significant adder is called a ripple carry adder.. The greater the number of bits that a ripple carry adder must add, the greater the time required for it to perform a valid addition. If two numbers are added such that no carries occur between stages, then the add time is simply the propagation time through a single full-adder.

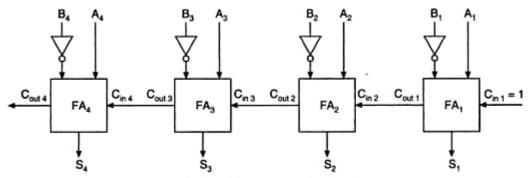

#### 4- Bit Parallel Subtractor:

The subtraction of binary numbers can be carried out most conveniently by means of complements, the subtraction A-B can be done by taking the 2's complement of B and adding it to A. The 2's complement can be obtained by taking the 1's complement and adding 1 to the least significant pair of bits. The 1's complement can be implemented with inverters as

Logic diagram of a 4-bit parallel subtractor.

#### **Binary-Adder Subtractor:**

A 4-bit adder-subtractor, the addition and subtraction operations are combined into one circuit with one common binary adder. This is done by including an X-OR gate with each full-adder. The mode input M controls the operation. When M=0, the circuit is an adder, and when M=1, the circuit becomes a subtractor. Each X-OR gate receives input M and one of the inputs of B. When M=0, E = 0=B. The full-adder receives the value of B, the input carry is 0

and the circuit performs A+B. when  $B \oplus 1 = B'$  and  $C_1 = 1$ . The B inputs are complemented and a 1 is through the input carry. The circuit performs the operation A plus the 2's complement of B.

Logic diagram of a 4-bit binary adder-subtractor.

#### The Look-Ahead —Carry Adder:

In parallel-adder, the speed with which an addition can be performed is governed by the time required for the carries to propagate or ripple through all of the stages of the adder. The look-ahead carry adder speeds up the process by eliminating this ripple carry delay. It examines all the input bits simultaneously and also generates the carry-in bits for all the stages simultaneously.

The method of speeding up the addition process is based on the two additional functions of the full-adder, called the carry generate and carry propagate functions.

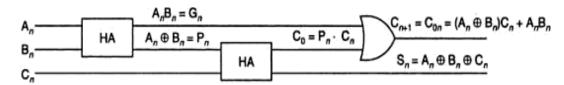

Consider one full adder stage; say the nth stage of a parallel adder as shown in fig. we know that is made by two half adders and that the half adder contains an X-OR gate to produce the sum and an AND gate to produce the carry. If both the bits  $A_n$  and  $B_n$  are 1s, a carry has to be generated in this stage regardless of whether the input carry  $C_{in}$  is a 0 or a 1. This is called generated carry, expressed as  $G_n = A_n.B_n$  which has to appear at the output through the OR gate as shown in fig.

A full adder (nth stage of a parallel adder).

There is another possibility of producing a carry out. X-OR gate inside the half-adder at the input produces an intermediary sum bit-call it  $P_n$  —which is expressed as  $P_n = A_n \oplus B_n$ . Next  $P_n$  and  $C_n$  are added using the X-OR gate inside the second half adder to produce the final

Consider the case of both  $P_n$  and  $C_n$  being 1. The input carry  $C_n$  has to be propagated to the output only if  $P_n$  is 1. If  $P_n$  is 0, even if  $C_n$  is 1, the and gate in the second half-adder will inhibit  $C_n$ . the carry out of the nth stage is 1 when either  $G_n=1$  or  $P_n.C_n=1$  or both  $G_n$  and  $P_n.C_n$  are equal to 1.

For the final sum and carry outputs of the nth stage, we get the following Boolean expressions.

$$S_n = P_n \oplus C_n$$

where  $P_n = A_n \oplus B_n$

$C_{on} = C_{n+1} = G_n + P_n C_n$  where  $G_n = A_n \cdot B_n$

Observe the recursive nature of the expression for the output carry at the nth stage which becomes the input carry for the (n+1)st stage .it is possible to express the output carry of a higher significant stage is the carry-out of the previous stage.

Based on these, the expression for the carry-outs of various full adders are as follows,

$$\begin{split} & C_1 = G_0 + P_0 \cdot C_0 \\ & C_2 = G_1 + P_1 \cdot C_1 = G_1 + P_1 \cdot G_0 + P_1 \cdot P_0 \cdot C_0 \\ & C_3 = G_2 + P_2 \cdot C_2 = G_2 + P_2 \cdot G_1 + P_2 \cdot P_1 \cdot G_0 + P_2 \cdot P_1 \cdot P_0 \cdot C_0 \\ & C_4 = G_3 + P_3 \cdot C_3 = G_3 + P_3 \cdot G_2 + P_3 \cdot P_2 \cdot G_1 + P_3 \cdot P_2 \cdot P_1 \cdot G_0 + P_3 \cdot P_2 \cdot P_1 \cdot P_0 \cdot C_0 \\ & The general expression for \textit{n} stages designated as 0 through (n-1) would be \\ & C_n = G_{n-1} + P_{n-1} \cdot C_{n-1} = G_{n-1} + P_{n-1} \cdot G_{n-2} + P_{n-1} \cdot P_{n-2} \cdot G_{n-3} + \dots + P_{n-1} \cdot \dots \cdot P_0 \cdot C_0 \end{split}$$

Observe that the final output carry is expressed as a function of the input variables in SOP form. Which is two level AND-OR or equivalent NAND-NAND form. Observe that the full look-ahead scheme requires the use of OR gate with (n+1) inputs and AND gates with number of inputs varying from 2 to (n+1).

#### BCD Adder:

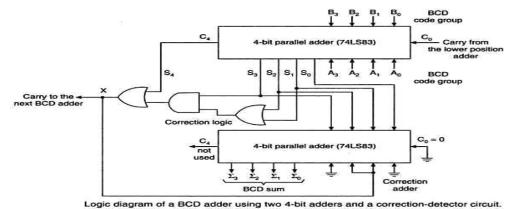

The BCD addition process:

- 1. Add the 4-bit BCD code groups for each decimal digit position using ordinary binary addition.

- 2. For those positions where the sum is 9 or less, the sum is in proper BCD form and no correction is needed.

- 3. When the sum of two digits is greater than 9, a correction of 0110 should be added to that sum, to produce the proper BCD result. This will produce a carry to be added to the next decimal position.

A BCD adder circuit must be able to operate in accordance with the above steps. In other words, the circuit must be able to do the following:

- 1. Add two 4-bit BCD code groups, using straight binary addition.

- 2. Determine, if the sum of this addition is greater than 1101 (decimal 9); if it is, add 0110 (decimal 6) to this sum and generate a carry to the next decimal position.

The first requirement is easily met by using a 4- bit binary parallel adder such as the 74LS83 IC .For example , if the two BCD code groups  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  are applied to a 4-bit parallel adder, the adder will output  $S_4S_3S_2S_1S_0$ , where  $S_4$  is actually  $C_4$ , the carry –out of the MSB bits.

The sum outputs  $S_4S_3S_2S_1S_0$  can range anywhere from 00000 to 100109 when both the BCD code groups are 1001=9). The circuitry for a BCD adder must include the logic needed to detect whenever the sum is greater than 01001, so that the correction can be added in. Those cases , where the sum is greater than 1001 are listed as:

| S <sub>4</sub> | S <sub>3</sub> | S <sub>2</sub> | S | S  | Decimal number |

|----------------|----------------|----------------|---|----|----------------|

| 0              | 1              | 0              | 1 | 0  | 10             |

| 0              | 1              | 0              | 1 | 1  | 11             |

| 0              | 1              | 1              | 0 | 0  | 12             |

| 0              | 1              | 1              | 0 | 1  | 13             |

| 0              | 1              | 1              | 1 | 0  | 14             |

| 0              | 1              | 1              | 1 | 1  | 15             |

| 1              | 0              | 0              | 0 | .0 | 16             |

| 1              | 0              | 0              | 0 | 1  | 17             |

| 1              | 0              | 0              | 1 | 0  | 18             |

Let us define a logic output X that will go HIGH only when the sum is greater than 01001 (i.e, for the cases in table). If examine these cases ,see that X will be HIGH for either of the following conditions:

- 1. Whenever S<sub>4</sub> =1(sum greater than15)

- 2. Whenever  $S_3 = 1$  and either  $S_2$  or  $S_1$  or both are 1 (sum 10 to

- 15) This condition can be expressed as

$$X=S_4+S_3(S_2+S_1)$$

Whenever X=1, it is necessary to add the correction factor 0110 to the sum bits, and to generate a carry. The circuit consists of three basic parts. The two BCD code groups  $A_3A_2A_1A_0$  and  $B_3B_2B_1B_0$  are added together in the upper 4-bit adder, to produce the sum  $S_4S_3S_2S_1S_0$ . The logic gates shown implement the expression for X. The lower 4-bit adder will add the correction 0110 to the sum bits, only when X=1, producing the final BCD sum output represented by  $\sum_3\sum_2\sum_1\sum_0$ . The X is also the carry-out that is produced when the sum is greater than 01001. When X=0, there is no carry and no addition of 0110. In such cases,  $\sum_3\sum_2\sum_1\sum_0=S_3S_2S_1S_0$ .

Two or more BCD adders can be connected in cascade when two or more digit decimal numbers are to be added. The carry-out of the first BCD adder is connected as the carry-in of the

second BCD adder, the carry-out of the second BCD adder is connected as the carry-in of the third BCD adder and so on.

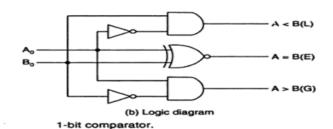

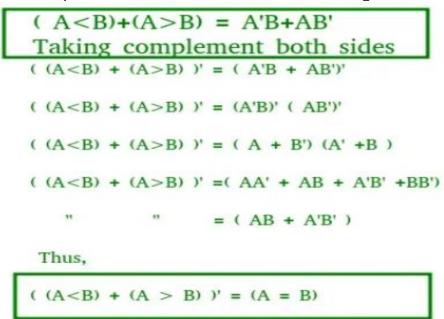

The logic for a 1-bit magnitude comparator: Let the 1-bit numbers be  $A = A_0$  and  $B = B_0$ . If  $A_0 = 1$  and  $B_0 = 0$ , then A > B. Therefore,

$$A > B$$

:  $G = A_0 \overline{B}_0$

If  $A_0 = 0$  and  $B_0 = 1$ , then A < B. Therefore,

$$A < B$$

:  $L = \overline{A}_0 B_0$

If  $A_0$  and  $B_0$  coincide, i.e.  $A_0 = B_0 = 0$  or if  $A_0 = B_0 = 1$ , then A = B. Therefore,

$$A = B : E = A_0 \odot B_0$$

| A <sub>o</sub> | Bo | L | E | G |

|----------------|----|---|---|---|

| 0              | 0  | 0 | 1 | 0 |

| 0              | 1  | 1 | 0 | 0 |

| 1              | 0  | 0 | 0 | 1 |

| 1              | 1  | 0 | 1 | 0 |

#### 1. Magnitude Comparator:

#### 1- bit Magnitude Comparator:

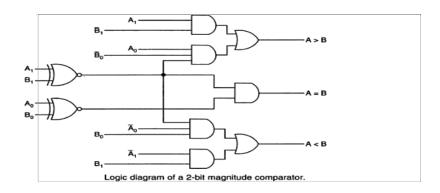

The logic for a 2-bit magnitude comparator: Let the two 2-bit numbers be  $A = A_1 A_0$  and  $B = B_1 B_0$ .

- 1. If  $A_1 = 1$  and  $B_1 = 0$ , then A > B or

- 2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 1$  and  $B_0 = 0$ , then A > B. So the logic expression for A > B is

$$A > B : G = A_1 \overline{B}_1 + (A_1 \odot B_1) A_0 \overline{B}_0$$

- 1. If  $A_1 = 0$  and  $B_1 = 1$ , then A < B or

- 2. If  $A_1$  and  $B_1$  coincide and  $A_0 = 0$  and  $B_0 = 1$ , then A < B. So the expression for A < B is

$$\mathsf{A} < \mathsf{B} : \mathsf{L} = \overline{\mathsf{A}}_{\mathsf{I}} \mathsf{B}_{\mathsf{I}} + (\mathsf{A}_{\mathsf{I}} \odot \mathsf{B}_{\mathsf{I}}) \overline{\mathsf{A}}_{\mathsf{0}} \mathsf{B}_{\mathsf{0}}$$

If  $A_1$  and  $B_1$  coincide and if  $A_0$  and  $B_0$  coincide then A = B. So the expression for A = B is

$$\mathsf{A} = \mathsf{B} : \mathsf{E} = (\mathsf{A}_1 \odot \mathsf{B}_1)(\mathsf{A}_0 \odot \mathsf{B}_0)$$

#### 4- Bit MagnitudeComparator:

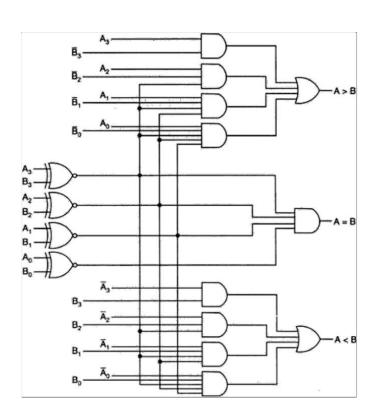

The logic for a 4-bit magnitude comparator: Let the two 4-bit numbers be  $A = A_3 A_2 A_1 A_0$  and  $B = B_3 B_2 B_1 B_0$ .

- 1. If  $A_3 = 1$  and  $B_3 = 0$ , then A > B. Or

- 2. If  $A_3$  and  $B_3$  coincide, and if  $A_2 = 1$  and  $B_2 = 0$ , then A > B. Or

- 3. If  $A_3$  and  $B_3$  coincide, and if  $A_2$  and  $B_2$  coincide, and if  $A_1 = 1$  and  $B_1 = 0$ , then A > B. Or

- If A<sub>3</sub> and B<sub>3</sub> coincide, and if A<sub>2</sub> and B<sub>2</sub> coincide, and if A<sub>1</sub> and B<sub>1</sub> coincide, and if A<sub>0</sub> = 1 and B<sub>0</sub> = 0, then A > B.

From these statements, we see that the logic expression for A > B can be written as

$$(A > B) = A_3 \overline{B}_3 + (A_3 \odot B_3) A_2 \overline{B}_2 + (A_3 \odot B_3) (A_2 \odot B_2) A_1 \overline{B}_1 + (A_3 \odot B_3) (A_2 \odot B_2) (A_1 \odot B_1) A_0 \overline{B}_0$$

Similarly, the logic expression for A < B can be written as

$$A < B = \overline{A}_3 B_3 + (A_3 \odot B_3) \overline{A}_2 B_2 + (A_3 \odot B_3) (A_2 \odot B_2) \overline{A}_1 B_1 + (A_3 \odot B_3) (A_2 \odot B_2) (A_1 \odot B_1) \overline{A}_0 B_0$$

If A<sub>3</sub> and B<sub>3</sub> coincide and if A<sub>2</sub> and B<sub>2</sub> coincide and if A<sub>1</sub> and B<sub>1</sub> coincide and if A<sub>0</sub> and B<sub>0</sub> coincide, then A = B.

So the expression for A = B can be written as

$$(A = B) = (A_1 \odot B_2)(A_2 \odot B_2)(A_1 \odot B_1)(A_0 \odot B_0)$$

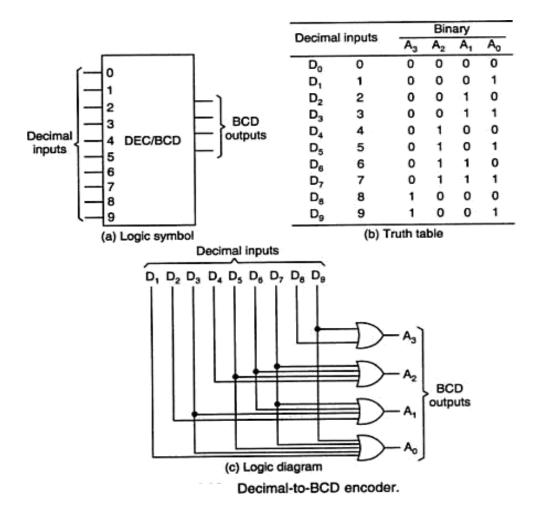

#### **Decimal to BCD Encoder:**

#### Tristate bus system:

In digital electronics**three-state**, **tri-state**, or **3-state**logic allows an output port to assume a high impedance state in addition to the 0 and 1 logic levels, effectively removing the output from the circuit.

This allows multiple circuits to share the same output line or lines (such as a bus which cannot listen to more than one device at a time).

Three-state outputs are implemented in many registers, bus drivers, and flip-flops in the 7400 and 4000 series as well as in other types, but also internally in many integrated circuits. Other typical uses are internal and external buses in microprocessors, computer memory, and peripherals. Many devices are controlled by an active-low input called OE (Output Enable) which dictates whether the outputs should be held in a high-impedance state or drive their respective loads (to either 0- or 1-level).

# **Magnitude Comparator in Digital Logic**

A magnitude digital Comparator is a combinational circuit that **compares two digital or binary numbers** in order to find out whether one binary number is equal, less than, or greater than the other binary number. We logically design a circuit for which we will have two inputs one for A and the other for B and have three output terminals, one for A > B condition, one for A = B condition, and one for A < B condition.

#### What is Magnitude Comparator?

Magnitude comparator is a type of <u>Combinational circuit</u>, It Basically compares two binary numbers and determines their relative magnitude. It gives output whether one number is greater than the other, or less than or equal. These comparators are used in digital systems, such as for sorting networks, and decision-making circuits to handle numerical comparisons perfectly without any error.

The circuit works by comparing the bits of the two numbers starting from the <u>most significant bit (MSB)</u> and moving toward the <u>least significant bit (LSB)</u>. At each bit position, the two corresponding bits of the numbers are compared. If the bit in the first number is greater than the corresponding bit in the second number, **the A>B output is set to 1**, and the circuit immediately determines that the first number is greater than the second. Similarly, if the bit in the second number is greater than the corresponding bit in the first number, **the A<B output is set to 1**, and the circuit immediately determines that the first number is less than the second.

Aiming for a top All India Rank in GATE CS & IT 2025 exam, but not sure where you stand?

We've got you covered! FREE GATE CS & IT Test Series - 2025 is designed to give you the edge you need. With previous year questions, subject-wise and full-length mock tests, and All India Mock Test, you can get a real feel of the exam. Plus, get our live mentorship classes with experts and attend live doubt-solving sessions to clear all your queries.

If the two corresponding bits are equal, the circuit moves to the next bit position and compares the next pair of bits. This process continues until all the bits have been compared. If at any point in the comparison, the circuit determines that the first number is greater or less than the second number, the comparison is terminated, and the appropriate output is generated.

If all the bits are equal, the circuit generates an **A=B output**, indicating that the two numbers are equal.

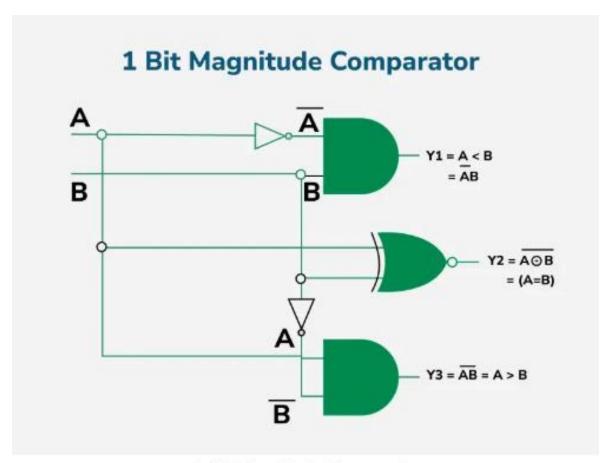

# **1-Bit Magnitude Comparator**

A comparator used to compare two bits is called a single-bit comparator. It consists of two inputs each for two single-bit numbers and three outputs to generate less than, equal to, and greater than between two binary numbers.

The truth table for a 1-bit comparator is given below.

| A | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | 1   | 0   |

| 0 | 1 | 1                                            | 0   | 0   |

| 1 | 0 | 0                                            | 0   | 1   |

| 1 | 1 | 0                                            | 1   | 0   |

From the above truth table logical expressions for each output can be expressed as follows.

A>B: AB' A<B: A'B A=B: A'B' + AB

From the above expressions, we can derive the following formula.

Derivation of 1-Bit Magnitude Comparator

By using these Boolean expressions, we can implement a logic circuit for this comparator as given below.

1 Bit Magnitude Comparator

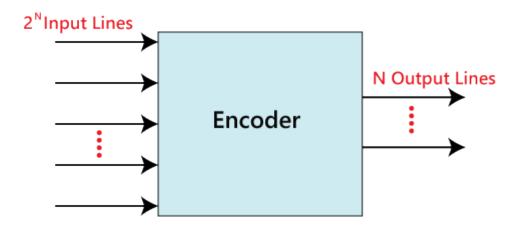

# **Encoders**

The combinational circuits that change the binary information into N output lines are known as **Encoders**. The binary information is passed in the form of  $2^N$  input lines. The output lines define the N-bit code for the binary information. In simple words, the **Encoder** performs the reverse operation of the **Decoder**. At a time, only one input line is activated for simplicity. The produced N-bit output code is equivalent to the binary information.

There are various types of encoders which are as follows:

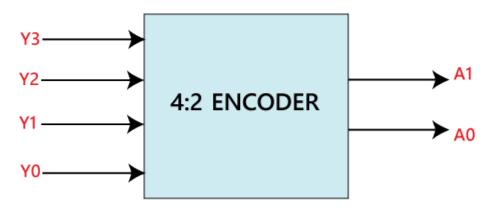

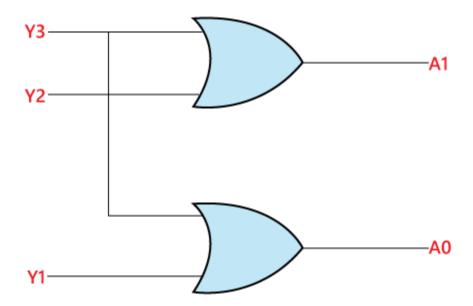

### 4 to 2 line Encoder:

In 4 to 2 line encoder, there are total of four inputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ , and two outputs, i.e.,  $A_0$  and  $A_1$ . In 4-input lines, one input-line is set to true at a time to get the respective binary code in the output side. Below are the block diagram and the truth table of the 4 to 2 line encoder.

### Block Diagram:

Truth Table:

|                       | INF            | OUTF           | PUTS           |                |                |

|-----------------------|----------------|----------------|----------------|----------------|----------------|

| <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Y <sub>1</sub> | Υ <sub>0</sub> | A <sub>1</sub> | A <sub>0</sub> |

| 1                     | 0              | 0              | 0              | 0              | 0              |

| 0                     | 1              | 0              | 0              | 0              | 1              |

| 0                     | 0              | 1              | 0              | 1              | 0              |

| 0                     | 0              | 0              | 1              | 1              | 1              |

The logical expression of the term A0 and A1 is as follows:

$$A_1 = Y_3 + Y_2$$

$A_0 = Y_3 + Y_1$

$$A_0 = Y_3 + Y_1$$

Logical circuit of the above expressions is given below:

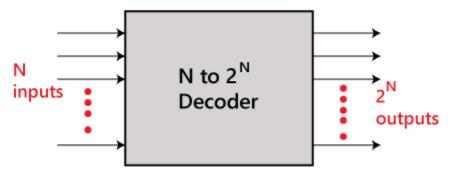

## Decoder

The combinational circuit that change the binary information into  $2^N$  output lines is known as **Decoders.** The binary information is passed in the form of N input lines. The output lines define the  $2^N$ -bit code for the binary information. In simple words, the **Decoder** performs the reverse operation of the **Encoder**. At a time, only one input line is activated for simplicity. The produced  $2^N$ -bit output code is equivalent to the binary information.

There are various types of decoders which are as follows:

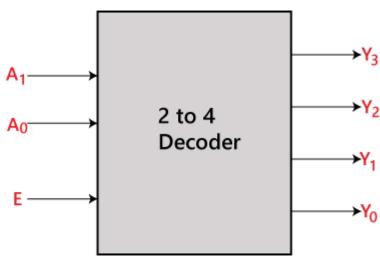

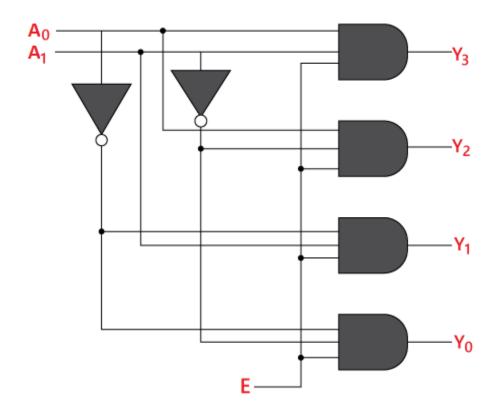

### 2 to 4 line decoder:

In the 2 to 4 line decoder, there is a total of three inputs, i.e.,  $A_0$ , and  $A_1$  and E and four outputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ . For each combination of inputs, when the enable 'E' is set to 1, one of these four outputs will be 1. The block diagram and the truth table of the 2 to 4 line decoder are given below.

### Block Diagram:

Truth Table:

| Enable | Enable INPU    |                | JTS OUTPUTS           |                |                |                       |

|--------|----------------|----------------|-----------------------|----------------|----------------|-----------------------|

| E      | A <sub>1</sub> | A <sub>0</sub> | <b>Y</b> <sub>3</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | <b>Y</b> <sub>0</sub> |

| 0      | Х              | Х              | 0                     | 0              | 0              | 0                     |

| 1      | 0              | 0              | 0                     | 0              | 0              | 1                     |

| 1      | 0              | 1              | 0                     | 0              | 1              | 0                     |

| 1      | 1              | 0              | 0                     | 1              | 0              | 0                     |

| 1      | 1              | 1              | 1                     | 0              | 0              | 0                     |

The logical expression of the term Y0, Y0, Y2, and Y3 is as follows:

$Y_3=E.A_1.A_0$   $Y_2=E.A_1.A_0'$

$Y_1=E.A_1'.A_0$   $Y_0=E.A_1'.A_0'$

Logical circuit of the above expressions is given below:

# Multiplexer

A multiplexer is a combinational circuit that has 2<sup>n</sup> input lines and a single output line. Simply, the multiplexer is a multi-input and single-output combinational circuit. The binary information is received from the input lines and directed to the output line. On the basis of the values of the selection lines, one of these data inputs will be connected to the output.

Unlike encoder and decoder, there are n selection lines and  $2^n$  input lines. So, there is a total of  $2^n$  possible combinations of inputs. A multiplexer is also treated as **Mux**.

There are various types of the multiplexer which are as follows:

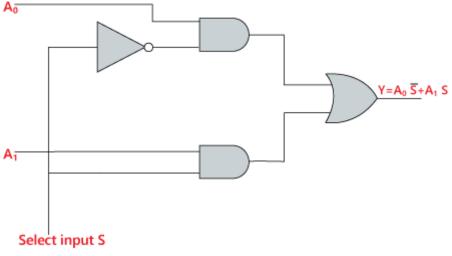

### 2×1 Multiplexer:

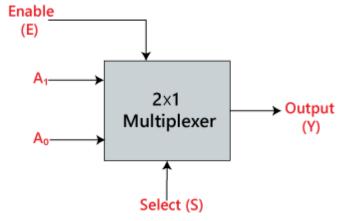

In  $2\times1$  multiplexer, there are only two inputs, i.e.,  $A_0$  and  $A_1$ , 1 selection line, i.e.,  $S_0$  and single outputs, i.e., Y. On the basis of the combination of inputs which are present at the selection line  $S^0$ , one of these 2 inputs will be connected to the output. The block diagram and the truth table of the  $2\times1$  multiplexer are given below.

#### Backward Skip 10sPlay VideoForward Skip 10s

### Block Diagram:

**Truth Table:**

| INPUTS         | Output         |

|----------------|----------------|

| S <sub>0</sub> | Y              |

| 0              | A <sub>0</sub> |

| 1              | A <sub>1</sub> |

The logical expression of the term Y is as follows:

$$Y=S_0'.A_0+S_0.A_1$$

Logical circuit of the above expression is given below:

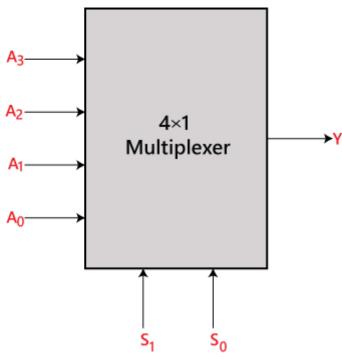

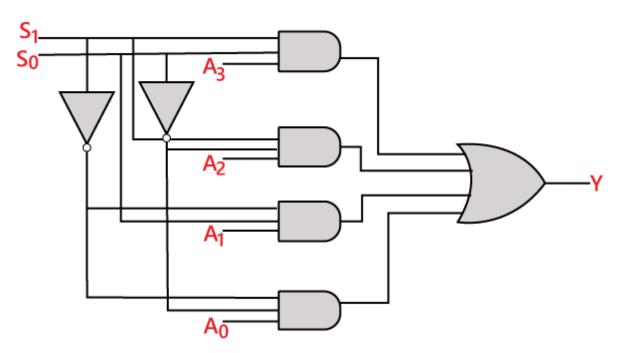

# 4x1 Multiplexer:

In the  $4\times1$  multiplexer, there is a total of four inputs, i.e.,  $A_0$ ,  $A_1$ ,  $A_2$ , and  $A_3$ , 2 selection lines, i.e.,  $S_0$  and  $S_1$  and single output, i.e., Y. On the basis of the combination of inputs that are present at the selection lines  $S^0$  and  $S_1$ , one of these 4 inputs are connected to the output. The block diagram and the truth table of the  $4\times1$  multiplexer are given below.

### Block Diagram:

Truth Table:

| INP | Output                        |                |  |

|-----|-------------------------------|----------------|--|

| Sı  | S <sub>1</sub> S <sub>0</sub> |                |  |

| 0   | 0                             | A <sub>0</sub> |  |

| 0   | 1                             | A <sub>1</sub> |  |

| 1   | 0                             | A <sub>2</sub> |  |

| 1   | 1                             | A <sub>3</sub> |  |

The logical expression of the term Y is as follows:

$$Y=S_1'S_0'A_0+S_1'S_0A_1+S_1S_0'A_2+S_1S_0A_3$$

Logical circuit of the above expression is given below:

# De-multiplexer

A De-multiplexer is a combinational circuit that has only 1 input line and  $2^{\mathbb{N}}$  output lines. Simply, the multiplexer is a single-input and multi-output combinational circuit. The information is received from the single input lines and directed to the output line. On the basis of the values of the selection lines, the input will be connected to one of these outputs. De-multiplexer is opposite to the multiplexer.

Unlike encoder and decoder, there are n selection lines and 2<sup>n</sup> outputs. So, there is a total of 2<sup>n</sup> possible combinations of inputs. De-multiplexer is also treated as **De-mux**.

There are various types of De-multiplexer which are as follows:

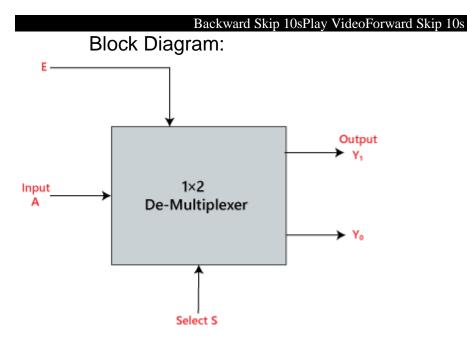

# 1x2 De-multiplexer:

In the 1 to 2 De-multiplexer, there are only two outputs, i.e.,  $Y_0$ , and  $Y_1$ , 1 selection lines, i.e.,  $S_0$ , and single input, i.e., A. On the basis of the selection value, the input will be connected to one of the outputs. The block diagram and the truth table of the  $1 \times 2$  multiplexer are given below.

Truth Table:

| INPUTS         | Output         |                |  |

|----------------|----------------|----------------|--|

| S <sub>0</sub> | Υ <sub>1</sub> | Y <sub>0</sub> |  |

| 0              | 0              | Α              |  |

| 1              | А              | 0              |  |

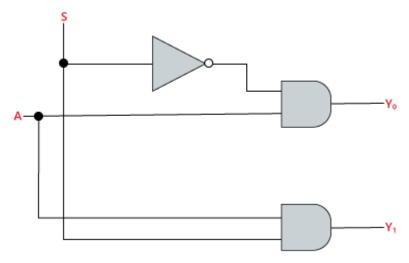

The logical expression of the term Y is as follows:

$$Y_0 = S_0'.A$$

$Y_1 = S_0.A$

Logical circuit of the above expressions is given below:

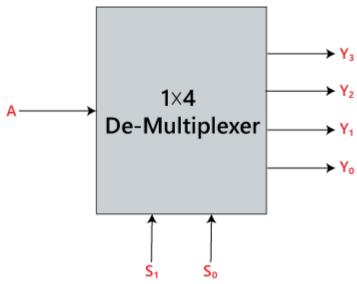

# 1x4 De-multiplexer:

In 1 to 4 De-multiplexer, there are total of four outputs, i.e.,  $Y_0$ ,  $Y_1$ ,  $Y_2$ , and  $Y_3$ , 2 selection lines, i.e.,  $S_0$  and  $S_1$  and single input, i.e., A. On the basis of the combination of inputs which are present at the selection lines  $S_0$  and  $S_1$ , the input be connected to one of the outputs. The block diagram and the truth table of the 1×4 multiplexer are given below.

### Block Diagram:

Truth Table:

| INP            | UTS            | Output         |                |                |                |  |

|----------------|----------------|----------------|----------------|----------------|----------------|--|

| S <sub>1</sub> | S <sub>0</sub> | Υ <sub>3</sub> | Y <sub>2</sub> | Υ <sub>1</sub> | Y <sub>0</sub> |  |

| 0              | 0              | 0              | 0              | 0              | А              |  |

| 0              | 1              | 0              | 0              | А              | 0              |  |

| 1              | 0              | 0              | А              | 0              | 0              |  |

| 1              | 1              | А              | 0              | 0              | 0              |  |

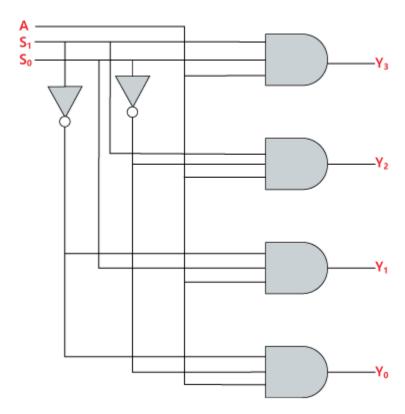

The logical expression of the term Y is as follows:

$Y_0=S_1' S_0' A$   $y_1=S_1' S_0 A$

$y_2=S_1 S_0' A$   $y_3=S_1 S_0 A$

ogical circuit of the above expressions is given below:

### **HDL Model of Combinational Circuits**

Any language from a class of computer languages and/or programming languages used for the formal description of digital logic and electronic circuits is known as a hardware description language, or HDL, in the field of electronics.

To create executable hardware specifications, HDLs are employed.

The capacity to simulate a piece of hardware before it is built physically is given to the hardware designer via simulation software that is written to embody the underlying semantics of the language statements and simulate time.

#### **HDL Models**

Any one of the following modeling approaches can be used to describe the Verilog HDL model of a combinational circuit:

- 1. Gate level modeling using instantiations of predefined and user-defined primitive gates.

- 2. Data flow modeling using continuous assignment with the keyword assign.

- 3. Behavioral modeling using procedural assignment statements with the keyword always.

### Gate level modeling:

A circuit of this type is identified by its logic gates and how they are connected. A schematic diagram's textual description is provided through gate-level modeling. Twelve fundamental gates are preset primitives in the Verilog HDL. They consist of and, NAND, OR, NOR, XOR, XNOR, NOT, & Buffer.

### Data flow modeling:

Combinational logic dataflow modeling employs a variety of operators that work on operands to yield desired outcomes. Around 30 distinct operators are offered by Verilog HDL. Continuous assignments and the phrase assign are used in dataflow modeling. A statement that gives a value to a net is known as a continuous assignment. Using the data type family net, a physical link between circuit components can be represented.

### **Behavioral modeling:**

A functional and algorithmic level representation of digital circuits is provided by behavioral modeling. Although it can also be used to describe combinational circuits, it is most frequently employed to explain sequential circuits. A list of procedural assignment statements is followed by an optional event control expression and the word always in behavioral descriptions.